DAFTAR ISI

Presettable counters adalah jenis counter yang dapat diatur ke nilai awal hitungan manapun, baik secara asynchronous (tanpa tergantung pada sinyal clock) maupun synchronous (dengan transisi aktif dari sinyal clock). Pengaturan awal ini dicapai dengan menggunakan input PRESET dan CLEAR (atau MASTER RESET) yang tersedia pada flip-flop. Operasi pengaturan awal ini juga dikenal sebagai operasi 'preloading' atau 'loading'.

2. TUJUAN[Back]

- Memahami prinsip kerja presettable counters.

- Mempelajari cara mengatur nilai awal hitungan pada presettable counters.

- Mengamati perbedaan antara presetting asynchronous dan synchronous.

- Menganalisis aplikasi presettable counters dalam rangkaian digital.

3. ALAT DAN BAHAN[Back]

ALAT

- Software Proteus 8.17

Proteus Design Suite adalah sebuah paket perangkat lunak (software suite) yang sangat populer dan serbaguna dalam bidang desain dan simulasi elektronik. Secara fundamental, Proteus menawarkan lingkungan terintegrasi untuk mendesain skematik rangkaian elektronik, melakukan simulasi fungsional dari rangkaian tersebut (termasuk simulasi mixed-mode untuk sirkuit analog dan digital), serta merancang layout Papan Sirkuit Tercetak (PCB) yang siap untuk manufaktur. Fitur unggulannya adalah kemampuan Virtual System Modelling (VSM), yang memungkinkan pengguna untuk mensimulasikan mikrokontroler beserta kode firmware-nya secara bersamaan dengan komponen elektronik lainnya, sehingga memungkinkan pengujian dan debugging sistem tertanam (embedded systems) secara virtual sebelum pembuatan prototipe fisik. Dengan perpustakaan komponen yang luas dan alat desain yang intuitif, Proteus menjadi pilihan utama bagi insinyur elektronik, teknisi, maupun pelajar untuk mempercepat proses desain, mengurangi biaya pengembangan, dan meminimalkan kesalahan dalam proyek elektronika.

BAHAN

- LOGIC STATE & LOGIC PROBE

Dalam dunia elektronika digital, logic state merujuk pada salah satu dari dua kondisi fundamental yang dapat dimiliki oleh sinyal digital: "tinggi" (high) atau "rendah" (low), yang secara konvensional direpresentasikan sebagai logika '1' dan logika '0'. Kondisi ini diwujudkan dalam level tegangan tertentu dalam sirkuit; misalnya, dalam sistem TTL (Transistor-Transistor Logic), logika '1' mungkin diwakili oleh tegangan sekitar +5 volt, sedangkan logika '0' oleh sekitar 0 volt. Perubahan antara dua logic state ini membentuk informasi yang diproses oleh sirkuit digital, menjadi dasar bagi semua operasi komputasi dan kontrol.

Untuk memverifikasi atau memecahkan masalah logic state dalam sirkuit, digunakan alat yang disebut logic probe. Sebuah logic probe adalah perangkat uji genggam berbiaya rendah yang dirancang khusus untuk menganalisis dan menampilkan logic state (boolean 0 atau 1) dari suatu titik dalam sirkuit digital. Umumnya, logic probe dilengkapi dengan beberapa indikator LED (Light Emitting Diode): satu LED (seringkali merah) untuk menunjukkan logic high (1), satu lagi (seringkali hijau) untuk logic low (0), dan terkadang LED ketiga (misalnya kuning atau oranye) yang menyala atau berkedip untuk menunjukkan adanya pulsa atau sinyal yang berosilasi. Beberapa logic probe yang lebih canggih bahkan dapat mendeteksi pulsa yang sangat singkat dan menyimpannya (pulse stretching) agar dapat terlihat, serta membedakan antara logic low dan kondisi tri-state (impedansi tinggi atau tidak terhubung) di mana tidak ada level logika yang jelas. Dengan menempelkan ujung probe ke titik tertentu di sirkuit, seorang teknisi dapat dengan cepat menentukan apakah sinyal pada titik tersebut berada dalam state logika yang benar sesuai dengan desain sirkuit.

- NAND-GATE

NAND adalah singkatan dari "NOT AND". Gerbang NAND dua masukan adalah rangkaian logika kombinasi digital yang melakukan kebalikan logika dari gerbang AND.

Sementara gerbang AND menghasilkan logika "1" hanya jika kedua masukannya berlogika "1", gerbang NAND menghasilkan logika "0" untuk kombinasi masukan yang sama. Simbol dan tabel kebenaran untuk gerbang NAND ditunjukkan pada Gambar 1. Ekspresi Boolean untuk gerbang NAND dengan dua masukan (A, B) dan keluaran X adalah:

Gerbang NAND membantu mendeteksi jika satu masukan ke sistem digital memiliki nilai rendah. Misalnya, sistem keamanan sederhana yang hanya terdiri dari gerbang NAND dapat digunakan untuk memantau status sensor yang terhubung ke jendela dan/atau pintu. Jika jendela/pintu tertutup, sensor mengirimkan sinyal logika "1" ke sistem keamanan. Saat semua jendela dan pintu tertutup, keluaran alarm adalah "0". Jika satu jendela atau pintu terbuka, keluaran sistem keamanan berubah status menjadi "1" dan ini dapat digunakan untuk memicu alarm atau melakukan tindakan lain.

Popularitas gerbang NAND berasal dari fakta bahwa gerbang ini merupakan operator logika digital yang paling mudah diimplementasikan menggunakan teknologi transistor, misalnya, gerbang NAND dua masukan hanya menggunakan empat transistor ketika diimplementasikan dalam CMOS. Semua operator logika lainnya dapat diimplementasikan hanya menggunakan gerbang NAND yang terhubung dalam konfigurasi yang berbeda. Mikroprosesor awal diimplementasikan hanya menggunakan rangkaian trivial ini.

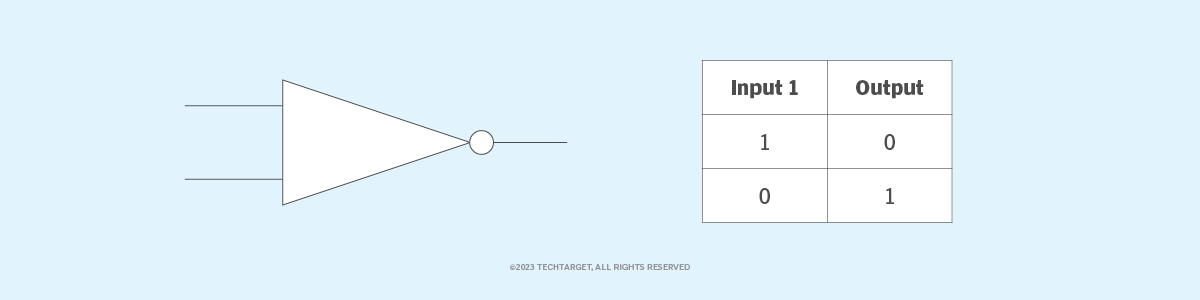

- NOT-GATE

Inverter logika, terkadang disebut gerbang NOT untuk membedakannya dari jenis perangkat inverter elektronik lainnya, hanya memiliki satu masukan. Gerbang NOT membalikkan keadaan logika. Jika masukan gerbang adalah 1, maka keluarannya adalah 0. Jika masukannya 0, maka keluarannya adalah 1. Sebagai salah satu gerbang logika yang menerima satu masukan dan menghasilkan satu keluaran, gerbang NOT juga merupakan salah satu yang paling sederhana karena hanya membalikkan masukan yang diberikan. Seperti ditunjukkan pada Gambar 4, tabel kebenaran untuk gerbang NOT sederhana.

- IC FLIP FLOP 74LS109

Chip 74×109 adalah flip-flop J-K ganda dengan kemampuan clear dan preset. Ini berarti chip ini berisi dua flip-flop J-K independen dalam satu chip, masing-masing memiliki input untuk J, K, clock (CP), dan output (Q dan Q̅). Selain itu, chip ini memiliki input clear (CLR) dan preset (PRE) untuk masing-masing flip-flop.

Berikut penjelasan sederhana tentang fungsi masing-masing masukan:

- Masukan J dan K' : Input ini mengontrol status flip-flop. K dibalik, artinya ketika J TINGGI dan K RENDAH, flip-flop akan mengubah statusnya saat ini pada tepi naik clock.

- Clock (CP) : Flip-flop memeriksa masukan J dan K dan mengubah status berdasarkan keduanya ketika tepi clock terjadi.

- Clear (CLR) : Input ini langsung mengatur keluaran Q ke RENDAH (0), terlepas dari masukan lainnya.

- Preset (PRE) : Input ini langsung mengatur keluaran Q ke TINGGI (1), terlepas dari masukan lainnya.

- Siapkan semua komponen yang dibutuhkan : LOGISTATE, LOGICPROBE, NOT-GATE, dan AND-GATE 3 Input

- Susun rangkaian sesuai dengan gambar : LOGICSTATE > NAND-GATE > IC Flip Flop 74LS109 > LOGICPROBE

- Simulasikan rangkaian dengan menekan tombol PLAY.

Fig 11.12

Prinsip kerja rangkaian ini adalah gabungan antara pencacah biner UP sinkron dan mekanisme prasetel asinkron, yang memungkinkan pencacah untuk menghitung naik dari nilai awal yang telah ditentukan.

Operasi Prasetel (Pemuatan Paralel):

Ketika masukan PL (Parallel Load) diaktifkan (diberi logika RENDAH), seluruh fungsi penghitungan berhenti sementara, dan rangkaian beralih ke mode pemuatan nilai. Sinyal PL yang rendah akan melewati sebuah inverter dan menghasilkan sinyal tinggi. Sinyal tinggi ini, bersama dengan nilai-nilai dari masukan prasetel (P0, P1, P2, P3), akan mengontrol masukan PRESET dan CLEAR (aktif RENDAH) dari setiap flip-flop (FF0-FF3) melalui konfigurasi gerbang NAND dan inverter. Jika Px adalah '1', PRESET dari FFx akan diaktifkan (menjadi RENDAH) sementara CLEAR tetap non-aktif (TINGGI), memaksa keluaran Qx menjadi '1'. Sebaliknya, jika Px adalah '0', CLEAR dari FFx akan diaktifkan (menjadi RENDAH) sementara PRESET tetap non-aktif (TINGGI), memaksa keluaran Qx menjadi '0'. Dengan demikian, nilai-nilai dari P3, P2, P1, P0 secara simultan dimuat ke dalam keluaran Q3, Q2, Q1, Q0, mengatur hitungan awal pencacah.

Operasi Pencacahan UP Sinkron:

Setelah PL dinonaktifkan (diberi logika TINGGI), rangkaian kembali ke mode pencacahan. Semua flip-flop (FF0-FF3) menerima sinyal Clock in yang sama secara bersamaan, menjadikannya pencacah sinkron. Flip-flop paling rendah (FF0) diatur untuk selalu toggle (mengubah keadaan Q-nya) pada setiap transisi aktif sinyal clock (biasanya tepi naik, karena 74LS109 adalah positive edge-triggered JK FF dengan J dan K dihubungkan ke VCC). Untuk flip-flop berikutnya (FF1, FF2, FF3), masukan J dan K mereka diatur berdasarkan kondisi keluaran Q dari flip-flop sebelumnya melalui gerbang logika (AND/NAND). Misalnya, FF1 hanya akan toggle ketika Q0 berada di keadaan '1' dan terjadi transisi clock. FF2 akan toggle ketika Q0 dan Q1 keduanya '1' dan terjadi transisi clock, dan seterusnya. Pola ini menciptakan urutan hitungan biner naik dari nilai prasetel (misalnya, 0, 1, 2, ..., 15). Keluaran Q dari setiap flip-flop (Q0, Q1, Q2, Q3) kemudian diumpankan ke dekoder BCD ke 7-segment (4511) yang menerjemahkan nilai biner menjadi format yang dapat ditampilkan pada 7-segment display.

6. FILE DOWNLOAD [Back]

Berikut ini adalah file Proteus terkait:

- Download 11.12 klik disini

- Download 11.13 klik disini

Berikut ini adalah datasheet terkait:

- Download IC FLIP FLOP 74LS109 klik disini

Komentar

Posting Komentar